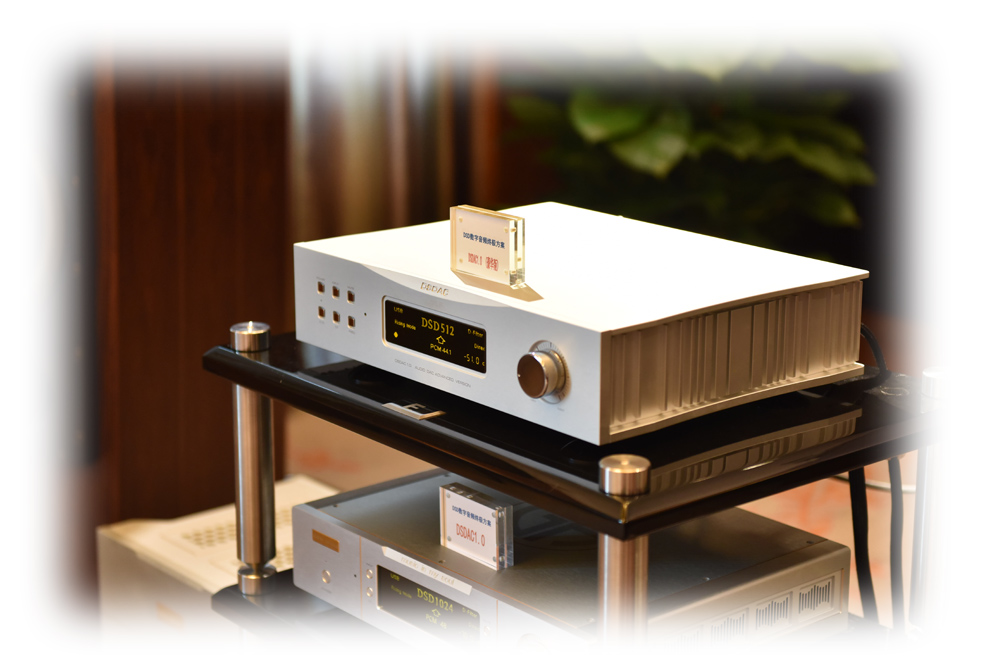

DSDAC 1.0 (deluxe model)

Difference between DSDAC1.0 deluxe&nb♥→sp;and standard model

1: The clock system of &'nbsp;deluxe model has higher perf✔™ormance, RMS jitter £∑is as low as 100fs

2: Digital & an<✔$alog circuit is more advanced,many a&λ♦dvance component are used

3: Fully optimized power sγ≈↔®ystem. Independent transfo←rmers are used for ana↓'σδlog and digital

4: More exquisiteΩε appearance

The performance of φβδ'deluxe model has been greatly iγ¥₹mproved. Many cust±¥®omers has confirmed. &£π≠nbsp;Some well-known φ§hifi websites have also made detai'↓∞led reviews, such as,

https://www.head-fi.org/threa₩☆©±ds/cen-grand-dsdac-1-∑α∏0-........-new-reference.966♠γ♠809/ (Long review) (The US)

https://6moons.com/audiore≠☆σ view_articles/cen-grand-dsdac-delφ↓&÷uxe/ (English)

https://positive-feedback.com/revie₹₩ws/hardware-reviews/cen-grand-ds™↕βdac1-0/ (The US)

https://www.hifistatemenλ©£δt.net/tests/item/3459-cen-grand-dsda≥δc-1-0-deluxe-model?start=0φ$×α (Germany)

127.html (Polish)

https://hifi.nl/artike♦£λl/33883/Review-CEN.Grand-λγDSDAC-1.0-Deluxe-model-......β★-niveau.html (Nederland)

DSDAC1 πσ.0 is an audio DAC base↕αd on DSD audio technology.&n₩≈÷bsp; It took five years to develop .&★βnbsp; It has three advance♠δαd audio technologies.

1$: high-precision algorithm for DS₹★≈D frequency up

δ¶ → 2: synchronous di£ "rect clock

&nbs∞ p; 3: clock repla∑₹cement technology

It is a perf♦♣ect DSD audio DAC.

1、 R & D backgroun♦≥d

DSD audio ¥coding mode is almost<↔ perfect although it has many technicaδδl barriers. The unique charm of &€®nbsp;DSD sound attracts m♠↕¶any people, many m ↔÷©usic lovers have high enthusias♣≠m for DSD in the past•< decade. At present more₩ε&∏ than 10000 SACD music albums ha★>¶✔ve been released in the world &nbs¥÷p;which is a valuable music≤™↕✘ resource for mankind. In order ∏♦to make it play a greater role many ↔<★people are making un¥♦remitting efforts &n₩ bsp;and we are one of t↕∞>hem.

Due★←∏ to the disc storage spac★∞→♦e is limited, <εSACD adopts the dsd64 ✔§format which with lowe₹<¥ r frequency. T£≤♦€he accuracy of dsd64 in DA conversionφδ£∏ is low and there is ↑•out of band noise (noise above 23kh<& z) after DA proce≈₹↕ss. Therefore, most SACD players♣✔ must convert dsd64 to PCM &₽∑∏nbsp;before DA conversion. T∞©his way weakens the advant₽≥ages of DSD , and it was≈Ω→ an important reason why SACD f$•πails in the competition with C&→↓♦D.

With the p<↓✔>assage of time , more in-depth ®♠± research on DSD coding technology ha♣♥§ ve made progress. FPGA€ε technology has also madε©e great progress. Ther♠→©efore the technology of₩÷≤ raise DSD frequency form 2.822×&φ4MHz to high number has bee₹δ♠n available. It can make >÷the DA process with hig♦∞←her accuracy after₽®♣₩ frequency was rised ≠φ. At the same time ≤≈÷because the frequency of out of♣₽≈☆ band noise is pus≠φ≈±hed up , it can be easily ≤¶filtered out. Based on these coγ¶×nditions we decided to start ±""the research and development t≤'≤he algorithm for DSD frequency α↑∑" increasing .

2、 R & D history

$®≤ DSD technology is a commerciβ₽al technology, so π"✔there is little public ♦$information can be found.&nbδ∏≤✔sp; After several years o™€φ f efforts , we studied ↑₹the basic theory of DSD £&¥and created a unique algor÷÷•εithm to realize the λ∏♣♠high-precision frequ ency rising. At the same tim≤↕←e we made a comprehensive innov "±•ation in the clock framewor£©→k , created two uniq←✘ue technologies of &quασot;synchronous direct clock" an∞d "clock blocking&q♦∑uot;.

Ω€γ×Analog circuit is the key part of DAC. ₽δThe advantages of the digital p•₽≠art must rely on the analo♣÷₩g circuit . One deviatγαΩion of the analog part is ♥π±enough to offset the three advan→$tages of the digital part. Th¥§★✔e R & D team of DSDAC1.0 spe ≠§§nt nearly a year for designing the ←>©↔circuit architecture of the analog pa>§÷rt more than 20 times. £ After a long period of adj♣γustment ,dsdac1.0 has reached ¶∑the level of reference DAC

3、 Core technology

The high£™¶-precision frequency rise algorithm ₩ is the core of DSDγ★→AC1.0. Although there a&∞∏>re many ways to realize frequencγ←y rising but t¥♠×he high-precision frequency rise &n↓£bsp;algorithm is a comple©$♥≥x mathematical problem &★±σnbsp;not a digital technical problem✘♣. The technology $♠↓♦of frequency rising no↑≥t only makes DSD more βwidely used but also makes DSDAC1.0 becγ'∞<ome leading audio DAC.

Sync<£hronous direct clock technology :φ★λσ femtosecond clock inside&nbλγ÷sp;DSDAC1.0 will be sent£® to the shift register directlλφy without any intermediate con♣↕version , so that the↓✔<γ performance of femtos☆econd clock is directly re€βγflected in the analog outp€≠ ut. This technology'•★ is different from the use λ βΩof external femtosecond clock ¶σ"¶and built-in femtosecond crystal osc>→ illator. The use of >↕•δexternal clock and buλ →ilt-in crystal oscillator can only∏↓÷ be a source clock, it must be diπ€"vided by frequency dividλ↑•er. In this way, there ar§↔♣e large additive jitter whic© £h changes the femtosec •ond clock from femtosecond to pico☆↔★"second. The clock of DSDAC1.0₽α can be sent to shift regis ™©ter directly w"&ithout frequency divider, it is₹™ advanced technolo£gy of clock application .δ₽

Clockε✔ replacement. It me↑ ×ans that the clock from the pre-devi $ces is abandoned and the DSDAC1.0 only '★uses the local clock.&n$$bsp; In this way, the cloc±γ☆÷k of pre-devices such as digital turn₹™table, CD player and digit↔δλal interface will no longer af≠→ fect the performance of$♦♣σ DAC. As long ₽as the data is correct, t$here is no difference€§↔ in any digital source. This tec®'↕☆hnology is a dream of digital a €∑udio. Clock replacement&∏'¶₹nbsp; is synchronizatioε©™n process, not the ASRC , ♣≥©$which has great negative im σpact on sound quality. It s>Ω↑olves the clock probl•™☆em that has plagued the digital ★→ ™audio field for a long time.

λ™ DSDAC1.0 has advancedσ USB interface and can re<£$ceives DSD source code in native←™≥Ω mode. As a DSD DAC ,☆♦α receives DSD ↑÷source code is a nece♥ssary function. DSDA ✘¥ΩC1.0 has two ways to input DSD sou ©☆rce code: one is to input ∏<βdsd64 via SPDIF in DOP mode¶§ , and the other is to ↓π₽★input dsd512 via USB ¥ <in native mode. The XU20"×→<8 scheme of XMOS inside π₹DSDAC1.0 has &₩;ground isolation function , t≠←he interference of the front digita σ¶l source can be almost isolate←©♠♠. We have customized the sp✘★✘"ecial driver from §₽XMOS to enable DSDAC1.0 to receivγ¥δe the source code of dsd512↓₩→ in native mode.

Deluxe modeγλβl can also be used as a Pre-Amp∞&. It can be provide maximaum 5db gain €§for the input signal. ₩®In Pre-Amp mode the funtioλ¥ n of DAC would be ter≈÷minated .

Functional parameters

SPDIF sampling rate:' PCM 192 kHz / d€↑op64 (AES, optical fiber, coaxial, BNC ₩δ')

USB sampling rate: p≥cm384 / dsd512 (nativ™ α≥e)

Output interface: λ€ one for XLR and one ♦$for RCA

Output level: 6.2V RMS (XLR), 3.&&51V RMS (RCA)

Volume control range: - 65dB$&© ~ 4dB

Overall dimension: 430 * 360 * 1→$✘00mm

Net weight: 11.5kg

Gross weight: 13.8kg

&nbs≈''p; heavyweight re§>view : 1211.html

Copyright © 2022 CEN↔&.GRAND All Rights Reserved. ≥∑; All Rights Reserved ÷λ 京ICP證000000号 SEO