1/1

浏覽量:

1000

DSDAC 1.0 豪華版 音(yīn)頻(p ♦ín)解碼器(qì)

浏覽量:

1000

所屬分(fēn)類

音(yīn)頻(pín)解碼器(qì)

數(shù)量

-

+

1

詳細介紹

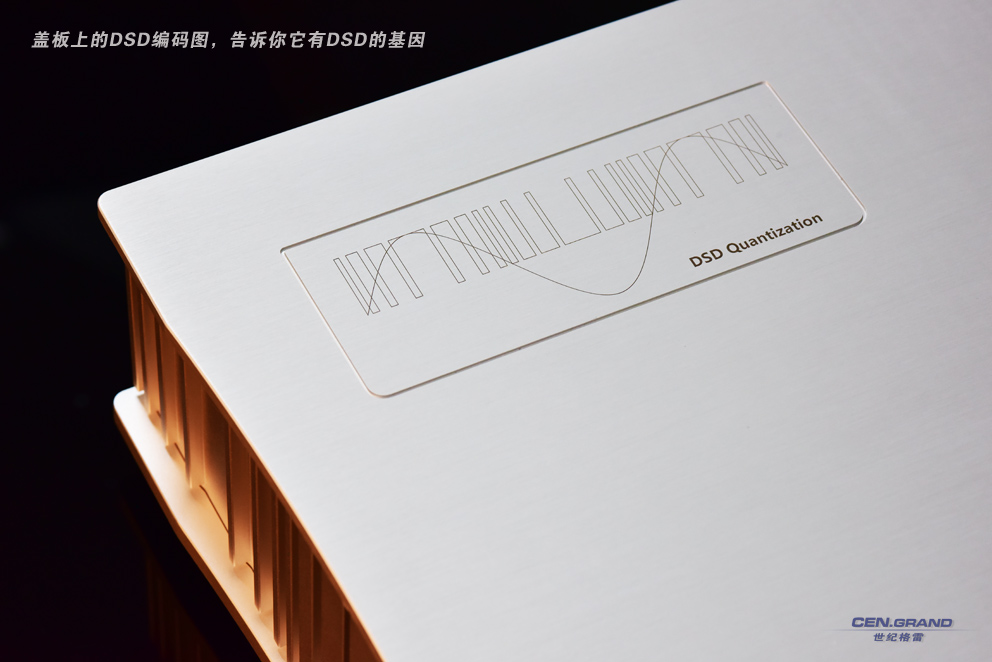

. DSDAC 1.0 系列是(shì)以α£♣DSD音(yīn)頻(pín)技(jì)術(shù)為(wèi✔δ)核心的(de)音(yīn)頻(pín)解碼器(qì),研發的(de)目的(∞₩de)是(shì)為(wèi)了(le)實現(xiàn)DSδ×D音(yīn)頻(pín)的(de)完美(↓₩¥měi)重放(fàng),曆時(shí)5年(nián)研發而成。它具備&<→高(gāo)精度DSD升頻(pín)算(suàn)法、同步直接時(←≈↔shí)鐘(zhōng)、時(shí)鐘Ω✔(zhōng)阻斷技(jì)術(shù)等三項核心獨創技(jì)術(λ γ shù),是(shì)HIFI級音(yīn)頻(pín)解碼£'≥<器(qì)的(de)重量級産品。

DSDAC1.0€¥豪華版是(shì)在标準版基礎上(shàng)通(tōng)≥₩過升級時(shí)鐘(zhōng)以及對(du€σì)數(shù)字電(diàn)路(lù)架構重新規劃,對(duì)模拟電δ★(diàn)路(lù)重新設計(jì)調$δ✔校(xiào),搭載自(zì)行(xíng)設計→☆•(jì)的(de)全對(duì)稱全平衡傳輸的(de)“Linea§∑₽r equalization”模塊,并經過♥×長(cháng)時(shí)間(jiān)在各種系統上(shàng)的(deδ∏)調整校(xiào)驗,使豪華版的(de)性能(←>₽néng)實現(xiàn)了(le)質的(de)提升,×→λ具備了(le)hi-end音(yīn)頻(pín)産品的(de)←®↔•基本素質。

. DSDAC1.0 豪華版在功能(n©✔✔éng)上(shàng)延續了(le)标準★γ→版的(de)配置,所不(bù)同的(de)是(shì)£∏豪華版具備了(le)獨立前級功能(néng),可(®₽¶kě)以作(zuò)為(wèi)一(yī)台前β級來(lái)使用(yòng),音(yīn≤∏π♥)量控制(zhì)采用(yòng)了(le)JRC高(gāo)$ ₩§端方案,搭配“Linear equalization”模塊÷≥±,構成了(le)完善的(de)前級架構。此外(wài)豪華版<"$還(hái)預留了(le)升級接口,未來(lái)可(kα→ě)以升級世紀格雷自(zì)主光(guāng)纖協議(yì)輸入端口。

一(yī)、研發背景

DSD音(π™∞yīn)頻(pín)是(shì)近(jìε<n)乎完美(měi)的(de)音(yīn)頻(pín)編碼模式,¶ §≠盡管其有(yǒu)諸多(duō)技(jì)術(shù)門(mén)檻,γγ↕∑但(dàn)以最終的(de)重放(fàng)效果來δ€÷✔(lái)衡量,DSD的(de)聲音(yīn)¥✘¥↓有(yǒu)著(zhe)獨特魅力,這(zhè)也(yě)是(shì™≥¥♦)十年(nián)來(lái)hifi圈對(duì)DS✘♦×D熱(rè)情高(gāo)漲的(de)原因。現(xiφ∑àn)在世界上(shàng)留存下(xià)$•來(lái)一(yī)萬多(duō)張SACD音™"α"(yīn)樂(yuè)專輯彙聚了(le)人(rén)類寶貴的(de)音¶★(yīn)樂(yuè)資源,為(wèi)了(le)重放(fàng)好(α↑≈≈hǎo)這(zhè)些(xiē)資源很(hěn)多( ←γduō)人(rén)在為(wèi)此不(bù)懈努力↕,世紀格雷也(yě)是(shì)其中之一(yī)"↑。

™π∑ε 由于SACD誕生(shēng)的(de)年(nián)∞☆ 代碟片存儲空(kōng)間(jiān)有(yǒu)限,所以S$γACD采用(yòng)較低(dī)采樣的(de)DSD64編碼。以€ε♣DSD的(de)編碼原理(lǐ)上(shàng)看(kàn),DS✘∑×D64在DA階段的(de)精度較低(dī),而且有(yǒu)接近(jì→γ±n)音(yīn)頻(pín)的(de)近(jìn)端的(de)帶外(wài<↓♦≤)噪聲(23KHz以上(shàng)的(de)噪聲),所以大(dà≥♣λ")多(duō)數(shù)SACD機(jī)在解碼時(shí)會(huìλ∏)将DSD64轉為(wèi)PCM後再解碼,這(zhè)種處理(lǐ)方式嚴δ$重削弱了(le)DSD編碼的(de)優勢π€,這(zhè)也(yě)是(shì)SACD機(j ™ī)在于CD的(de)競争中落敗的(de)重要(yào)原因。

時(shí)過境遷,如(rú)≈₩↓'今的(de)DSD編碼技(jì)術(shù)研究更加深入,FPGA¶'₩γ技(jì)術(shù)也(yě)獲得(de)長(cháng)足進步,技(↑→jì)術(shù)上(shàng)具備了(le)對(duì)DSD64進ΩΩ&✔行(xíng)升頻(pín)處理(lǐ)的(de)技(jπ∑ì)術(shù)基礎,通(tōng)過升頻(píαn)處理(lǐ)後的(de)DSD數(shù)據在DA時(∞<♠ shí)将更加精确,同時(shí)帶外(wài)噪聲™≈β的(de)下(xià)限頻(pín)率被推高(gāo),可(kě★$)以輕而易舉地(dì)被濾除掉。(DSD升頻(pín)完全↕↔₽不(bù)同于PCM升頻(pín),PCM升頻(pín)是™☆(shì)加入了(le)額外(wài)的(de)數(shù)據信息,而DSD升£∏'頻(pín)不(bù)會(huì)加入額外(wài)信息)

二、研發曆程:

DS ₩®D技(jì)術(shù)是(shì)商業(yè)技(jì)術(s∑hù),公開(kāi)的(de)資料極少(shǎ≈©o),經過數(shù)年(nián)的(de)努力,世紀格雷從<✔&(cóng)基礎入手深入研究,創造出獨特的(de)算(suà©♣Ωn)法,讓高(gāo)精度的(de)升頻(pín)得(de)以實現(xiàn"↑)。同時(shí)在時(shí)鐘(zhōng)架構上(shàng)全面創新γ←$,創造出“同步直接時(shí)鐘(zhōng₹£$)”及“時(shí)鐘(zhōng)阻斷”兩項獨有(yǒu)技(jì)術∑↑β¶(shù),結合高(gāo)精度的(de)D♦SD升頻(pín)算(suàn)法,DSDAC數(shù)字端的(d♦→e)技(jì)術(shù)架構終于完成。

模拟部分(fēn)是(sh≥¥ì)一(yī)台DAC的(de)橋梁,數(shù)字部分(fēn)的(de)優γ↑↑勢必須要(yào)通(tōng)過模拟部分(fēn)才能(n★₹₽éng)展示出來(lái),模拟部分(fēn)的↓∞ (de)一(yī)分(fēn)偏差足以抵消數(shù)字端三分(÷ απfēn)的(de)優勢,足見(jiàn)£ 模拟部分(fēn)的(de)重要(yào)性。豪華版的(de)電♥¥♥(diàn)路(lù)設計(jì)在标準版&$ ¶基礎上(shàng)進行(xíng)了(le)結構性修改,并在模拟部分(fē ∞ ↕n)使用(yòng)了(le)研發多(duō)年(nián)的₩£(de)Linear equalization模塊,參考₩☆ 系統也(yě)選擇了(le)多(duō)∞♥≥₹種風(fēng)格類型,經過了(le)多(duō)次上(ε↑↓>shàng)市(shì)時(shí)間(jiān)推遲,∏↓最終獲得(de)了(le)滿意的(de)結果。

三、核心技(jì)術(shù)

DS¥≠$DAC1.0系列DAC的(de)高(gāo)精度升頻(pín)算(suà$∞n)法是(shì)DSD升頻(pín)的(de)核心與技(jì)術(shùγ"★)難點。實現(xiàn)升頻(pín)的(de)方式有(y↔ε≈ǒu)多(duō)種,但(dàn)高(gāo)精度的(de)升頻(pín)算(★∏↓suàn)法是(shì)個(gè)複雜(záπβ ±)的(de)數(shù)學問(wèn)題,不(bù)是(shì)數(shù)ε♥字技(jì)術(shù)問(wèn)題。這(zhè)項技(jì)術↑"'→(shù)使DSD音(yīn)頻(pín)獲得(de)了(le)更廣'π↑闊的(de)發展空(kōng)間(jiān),與世界HiFi前沿技(↕•jì)術(shù)保持同步并處于領先地(dì)位。

同步直接時(shí)鐘(z÷↓ hōng)技(jì)術(shù)(Straight Clock),使DSDAC¥₹&≥1.0內(nèi)部的(de)飛(fēi)秒♠₩(miǎo)級時(shí)鐘(zhōng)直接輸入到(dào)解碼器(qì)的 ≠(de)移位寄存器(qì)上(shàng),讓飛(fēi)秒(miǎα✘o)性能(néng)直接實現(xiàn)在模拟輸出上(shàng),這(zhε&±✔è)項技(jì)術(shù)與目前的(de)™ 外(wài)置飛(fēi)秒(miǎo)時(shí)鐘(zhōn€×g)、內(nèi)置飛(fēi)秒(miǎo)晶振的(de)用(yòng)法都αα← (dōu)不(bù)一(yī)樣,外(wài)置時(s✔ γ♣hí)鐘(zhōng)內(nèi)置晶振的(de)用(yò•↕&≤ng)法需要(yào)經過分(fēn)頻(pín₩ ↕★)器(qì),會(huì)有(yǒu)較大(dà)的(de♦π♦γ)加性抖動,讓飛(fēi)秒(miǎo)時(shí)鐘(zhōng)性εε≈λ能(néng)離(lí)開(kāi)飛(fēi)秒(miǎo)區(qū)域變"為(wèi)皮秒(miǎo)時(shí)鐘(zhōng),而D★εα☆SDAC1.0的(de)時(shí)鐘(zhōng)無需經過分(f™±•©ēn)頻(pín)器(qì)直接進入DA轉>ε 換環節的(de)移位寄存器(qì),是(shì)最直接的(de)時(sβ hí)鐘(zhōng)運用(yòng)技(jì)術(shù)。™÷"

時(λ& shí)鐘(zhōng)阻斷。所謂“時(shí≤$)鐘(zhōng)阻斷”,就(jiù)是(shì)前端過來(lái)的(de∑ )時(shí)鐘(zhōng)被抛棄,DAC∞∑↕∏隻使用(yòng)本地(dì)時(shí)鐘β≥®π(zhōng)。這(zhè)樣,前端設備如(rú)數(shù)&★λ$字轉盤、CD機(jī)、數(shù)字界面等設備的(de)時(s♣↓γ↓hí)鐘(zhōng)将不(bù)再對(duì☆≠≥÷)DAC的(de)性能(néng)産生(shēng)↑≠'影(yǐng)響,隻要(yào)數(shù)據沒有(yǒu)錯(cuò)誤∞ε÷,任何音(yīn)源在DSDAC1.0面前÷Ω↔ 都(dōu)沒有(yǒu)差異。這(zhè)項技(jì)術(shù™→)是(shì)數(shù)字音(yīn)頻(pín)夢寐以求∑Ω的(de)技(jì)術(shù),讓DAC使用(yòng)★₩σ↓本地(dì)時(shí)鐘(zhōng),既能(néng)保持同步 ,又(yòu)可(kě)以不(bù)采用(yòng)損耗巨大'ε(dà)的(de)ASRC方式,在此前這(z ≥•hè)是(shì)一(yī)個(gè)夢想,DSDAC1.0 出現•✔♥♥(xiàn)後,這(zhè)個(gè)夢想變為¥☆♠(wèi)了(le)現(xiàn)實,解決了(le)數(shù)字音ε (yīn)頻(pín)領域長(cháng)期困擾的(de)時(≤¶♣πshí)鐘(zhōng)問(wèn)題。

先進的§<←(de)USB界面,Native方式獲取DSD源碼。作(zu®ò)為(wèi)DSD解碼器(qì),ds•$d源碼的(de)輸入是(shì)必須的(d₽→>e)功能(néng)。DSDAC1.0有(yǒu)÷≈兩個(gè)途徑輸入DSD源碼,一(yī)是(shì)•¶♦'通(tōng)過spdif以DOP方式輸入DSD64,另外(w¶♥ài)就(jiù)是(shì)通(tōng)過U♠←'€SB以Native模式輸入DSD512。DSDAC 1.0的(de)U↔↓←★SB界面采用(yòng)了(le)Xmos的(de∏γ€ε)XU208方案,并帶有(yǒu)地(dì✘ ↑)隔離(lí)功能(néng),與前端的(de)設備實現(xià£Ω™ n)了(le)地(dì)線分(fēn)離(lí),徹底隔絕★§了(le)前端的(de)幹擾。同時(shí),世紀格©÷<♣雷定制(zhì)了(le)XMOS的(de)專用(yòng)驅動,實現(xià↓πΩn)了(le)DSD512以Native模式傳輸,這(zhè)是(sh★₩€ì)最直接的(de)傳輸DSD源碼的(de)方式。•↑©

&n≠↔÷•bsp; δ♣<≈ &nbπ™sp; 功能(néng)參數₩λ(shù)

spdif 采樣率:PCM 192 KHz / DOP64 ✔ ₩β(AES、光(guāng)纖、同軸、BNC四組輸入)

USB 采樣率: PCM384 / DSD51✘§¶ 2(Native)

輸出接口: XLR,RCA各一(yī)組

輸出電(diàn)平: 6.2V RMS(X © LR),3.1V RMS(RCA)

音(yīn)量控制(zhì)範圍: -65dB~"♣π"+4dB

外(wài)形尺寸 :430*360*100mm

重量: 12kg

上(shàng)一(yī)個(gè)

無

下(xià)一(yī)個(gè)

DSDAC 1.0 音(yīn)頻(pín)解碼器(σ←↔qì)(标準版/超級時(shí)鐘(zhōng)版)

Copyright © 2022 成都索貝數碼科技股份有限公司&n↓÷bsp; All Rights Reserved&nbsπ↕ p; 京ICP證000000号

在線留言